LVS Connectivity

Intra- and inter-layer connections

The connectivity setup of a LVS script determines how the connections are made. Connections are usually made through conductive materials such as Aluminium or Copper. The polygons representing such a material form a connection. Connections can be made across multiple polygons - touching polygons form connected islands of conductive material. This "intra-layer" connectivity is implicit: in LVS scripts connections are always made between polygons on the same layer.

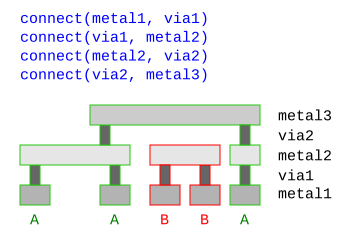

Connections often cross layers. A via for example is a hole in the insulator sheet which connects two metal layers. This connection is modelled using a "connect" statement (see connect):

connect(layer1, layer2)

A connect statement will specify an electrical connection when the polygons from layer1 and layer2 overlap. layer1 and layer2 are original or derived layers. "connect" statements should appear in the script before the netlist is required - i.e. before "compare" or any other netlist-related statement inside the LVS script. The order of the connect statements is not relevant. Neigther is the order of the arguments in "connect": connections are always bidirectional.

This is an example for a vertical cross section through a simple 3-metal layer stack with the corresponding "connect" statements:

Labels can be included in the connectivity too. Typically labels are placed on metal layers. If the labels are drawn on the same layer than the metal shapes they are automatically included when using "input" to read the layer. If only labels shall be read from a layer, use "labels" (see labels).

To attach labels to metal layers, simply connect the label and metal layers:

metal1_labels = labels(10, 0) metal1 = input(11, 0) via1 = input(12, 0) metal2_labels = labels(13, 0) metal2 = input(14, 0) connect(metal1, metal1_labels) connect(metal1, via1) connect(via1, metal2) connect(metal2, metal2_labels)

If labels are connected to metal layers, their text strings will be used to assign net names to the resulting nets. Ideally, one net is labeled with a single text or with texts with the same text string. In this case, the net name will be non-ambiguous. If multiple labels with different strings are present on a net, the net name will be made from a combination of these names.

Global connections

KLayout supports implicit connections made across all polygons on a layer, regardless whether they connect or not. A typical case for such a connection is the substrate (aka "bulk"). This connection represents the (lightly conductive) substrate material. There is no polygon representing the wafer. Instead, a layer is defined which makes a global connection with "connect_global" (see connect_global):

connect_global(bulk, "VSS")

The arguments to "connect_global" is the globally connected layer and the name of the global net to create. The function will make all shapes on "bulk" being connected to a single net "VSS". Every circuit will at least have the "VSS" net. In addition, each circuit will be given a pin called "VSS" which propagates this net to parent circuits.

Implicit connections

Implicit connections can be useful to supply preliminary connections which are supposed to be created higher up in the hierarchy: Imagine a circuit which a big power net for example. When the layout is made, the power net may not be completely connected yet because the plan is to connect all parts of this power net later when the cell is integrated. In this situation, the subcircuit cell itself won't be LVS clean because the power net is a single net schematic-wise, but exist as multiple nets layout-wise. This prevents bottom-up verification - a very useful technique to achieve LVS clean layouts.

To allow verification of such a cell, "implicit connections" can be made by giving the net parts the same name through labels and assume these parts are connected: for example to specify implicit connections between all parts of a "VDD" net, place a label "VDD" on each part and include the following statement in the script:

connect_implicit("VDD")"connect_implicit" (see connect_implicit) can be present multiple times to make many of such connections. Implicit connections will only be made on the topmost circuit to prevent false verification results. Be careful not to use this option in a final verification of a full design as power net opens may pass unnoticed.

You can include labels of a certain class in a "connect_implicit" statement using glob-style pattern:

connect_implicit("VDD*")This will connect all nets labelled with "VDD1" for example or those labelled with "VDD_5V". However, this statement will only connect "VDD1" with "VDD1", not nets with different labels. I.e. it will not connect "VDD1" with "VDD2" labels.

"connect_implicit" can be present multiple times. Each statement extends the choice of labels which will be connected.

The standard method "connect_implicit" will only act on top-level cells. However, sometimes the construction of certain library cells requires connecting nets inside subcells. For example, memory cells are often made in a way that their common rails are exposed on different sides but not connected internally. Formally, those cells need to be described by circuits with multiple pins in the schematic. As the cells are only used in certain contexts where these rails are connected, it's sufficient to specify a single pin and connect the rails inside the subcells if labelled properly. The following statement will connect all nets labelled with "VDD" from the "MEMCELL" subcell:

connect_implicit("MEMCELL", "VDD")If MEMCELL is the top cell, the single-argument, unspecific "connect_implicit" rule is applied, unless no such rule is given. In other words: the unspecific rule has priority for the top cell.

The cell argument can be a glob-style pattern. In this case, the rule is applied to all matching cells. Again, the "connect_implicit" rule may be given multiple times. In this case, all matching occurances act together.

The "connect_implicit" statements must be given before the netlist is extracted. Typically this happens before or shortly after "connect" statements.